# All Digital Phase Locked Loop design for different applications: A Review

Kunjal Parmar,

Student, Vishwakarma Government Engineering College

Chandkeda, Ahmedabad

Abstract- In this Brief, a review of various approaches to design the blocks of all digital phase locked loop (ADPLL) for specific application are presented. Today the most challenging task for designing the phase locked loop (PLL) is to achieve fast locking time and low jitter. In analog design the design complexity is increased. In this paper, advantages of all digital phase locked loop over analog phase locked loop is presented.

Index Terms- All digital phase locked loop (ADPLL), Phase locked loop (PLL)

#### I. INTRODUCTION

Nowadays the phase-locked loops (PLLs) are widely used in various applications. For example, a chip embedded with its own clock generator to provide the high-speed clock signal, clock recovery, and synchronization of chips and jitter and phase noise reduction. Traditionally, the PLL is composed of some analog blocks, e.g., charge pump and voltage-controlled oscillator (VCO). The leakage problem will become increasingly serious in advanced CMOS processes. As a result, the difficulty and the complexity of designing an analog PLL increase as the technology process advances [2].

There are many advantages of the all-digital phase locked loop (ADPLL) over analog PLL. ADPLLs have better noise immunity, better testability, programmability, stability, and portability over different processes [7], [8], [9] and they can reduce the system turnaround time. The analog PLL suffers from reduced supply voltage and increased gate leakage as the CMOS scaling in nanometer. Also the difficulty and complexity of analog PLL increases as the technology process advances. The ADPLL reduce the sensitivity to process voltage temperature variations, area and power consumption.

In this brief section II describes the basic architecture of ADPLL. Section III describes various approaches of design of ADPLL and section IV compares this approaches and section V discuss the conclusions.

## II. DESIGNS OF ADPLL

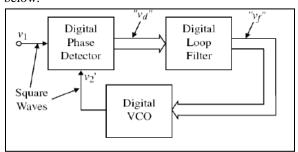

The basic architecture of ADPLL consists of phase frequency detector, digital loop filter, digital controlled oscillator and frequency divider in the feedback loop. The major component of ADPLL is the digital controlled oscillator. For the different applications the design of digital controlled oscillator has to be changed. The parameters of digital controlled oscillator are the operating frequency range, maximum operating frequency, frequency resolution. General block diagram of ADPLL is shown in Fig.1[6]. Various techniques used to design these blocks for specific application are describe as below.

Fig.1 Basic block diagram of ADPLL[6]

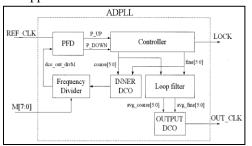

## A. Design of ADPLL for frequency synthesis

The architecture is to frequency synthesis application in the frequency range of 45-510MHz. In this approach [1] two DCO'S are used to reduce the output clock jitter. One DCO is used for tracking the reference clock and the other is used for generating the output clock. The adaptive search step is algorithm is used to find out target frequency. Loop filter is used to filter out the noise for further

improving jitter performance. Inner DCO has divided into two parts coarse tuning block and fine tuning block to increase the frequency resolution of the DCO. The DCO resolution is 5ps and rms jitter is near to 22ps and the power dissipation is 100mw in this approach.

Fig.2 ADPLL for frequency synthesis [1]

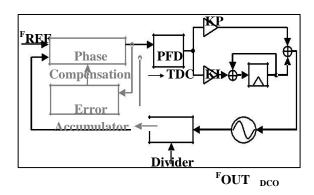

# B. <u>Design of ADPLL for Wireless</u> <u>communication</u>

In the wireless communication application the PLL has the large Phase error at the instant of frequency hopping, the loop is unable to compensate large phase error and output frequency is slowly updated. So this approach [2] is used to compensate this problem using dynamic phase controlled technique. In this technique to limit the growth of accumulated error, when phase error exceeds certain threshold, it is compensated by temporally changing divided ratio. This approach is to reduce the TDC noise without narrowing bandwidth and higher frequency locking time by using the KI controller. There are two TDC auxiliary and main, responsible for coarse and fine phase error detection. The frequency resolution of DCO can be increased by using delta sigma modulator at the input of DCO.

### **FCW**

Fig.3 ADPLL with phase compensation technique [2]

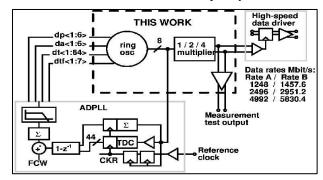

## C. <u>Design of ADPLL for clock generator of</u> multiple data rate

A clock generator for of MIPI M-PHY transmitter is presented in this approach [3]. In this, the low power with fine frequency resolution DCO is presented. The oscillator runs at the lower frequency range and higher frequency is obtained by using programmable low power frequency multiplier. Also quantization noise is reduce if the DCO frequency step size is minimized while the reference frequency constant.

Fig.4 ADPLL with frequency multiplier [3]

# D. <u>Design of ADPLL for high speed clock</u> generator

In this approach [4] the proposed parameterized DCO. The parameterized DCO can provide the maximum output frequency more than 1GHz and a wide operating frequency range. Also they developed an ADPLL compiler. By using this ADPLL compiler we could find out a low cost and low power DCO that meets user defined specification.

Fig.5 Parameterized DCO [4]

Parameterized DCO is formed with a loop including two parts the coarse tuning block ( $\beta$ -part) and the fine tuning block ( $\gamma$ -part). During frequency acquisition  $\beta$ -code selects the frequency and during phase acquisition  $\gamma$ -code decides the final output.

# E. <u>Design of ADPLL for distributed clock</u> generator

This paper [5] developed an ADPLL for the distributed clock generator based on networks of ADPLL. The architecture has a digital multi bit phase frequency detector. This digital PFD is required for synchronized operation of the ADPLL network in the context of distributed clock generator. Digital PFD has bang-bang PFD with time to digital converter and arithmetic block to produce the sign binary phase error.

Fig.6 Digital multi bit PFD [5]

## III. SUMMERY AND COMPARISON

|         | [1]    | [2]    | [3]    | [4]     |

|---------|--------|--------|--------|---------|

| Process | 0.35μ  | 180nm  | 40nm   | 180nm   |

|         | m      | CMOS   | CMOS   | CMOS    |

|         | CMOS   |        |        |         |

| Area    | 0.71m  |        | 0.012m | 0.084mm |

|         | $m^2$  |        | $m^2$  | 2       |

| Power   | 100m   | 18.6m  | 3.9mW  | 7.2mW   |

| Dissipa | W      | W      |        |         |

| tion    |        |        |        |         |

| Freque  | 45-    | 2.49G  | 1.248- | 96.1-   |

| ncy     | 510M   | Hz     | 5.83GH | 1014.6M |

| range   | Hz     |        | Z      | Hz      |

| Output  | 70ps   | 13.78p |        | 35.6ps  |

| jitter  |        | s      |        |         |

| Lock    | <46    | 5μs    |        |         |

| time    | cycles |        |        |         |

#### IV. CONCLUSIONS

In this paper the review of ADPLL is presented. Using two DCO we can increase the DCO resolution with wide frequency range. For large phase error detection with less locking time, phase compensation with error accumulation technique is used. Parameterized DCO which can generate more than 1GHz frequency is also presented. For low

power reduction in DCO the frequency multiplier is used with lower operating frequency range DCO. High precision PFD for ADPLL network is also presented.

#### V. ACKNOWLEDGEMENT

The author would like to thank MR. Bhavin Leuva for his technical support in this work

### **REFERENCES**

- [1] An All-Digital Phase-Locked Loop for High-Speed Clock Generation: Ching-Che Chung and Chen-Yi Lee; *IEEE* journal of solid-state circuits, vol. 38, no. 2, february 2003

- [2] An All-Digital Phase-Locked Loop with Dynamic Phase Control for Fast Locking Yun-Chen Chuang, Sung-Lin Tsai, Cheng-En Liu, and Tsung-Hsien Lin, IEEE Asian Solid-State Circuits Conference November 12-14, 2012/Kobe, Japan

- [3] A 1.2 6.4 GHz Clock Generator with a Low-Power DCO and Programmable Multiplier in 40-nm CMOS, Tero Tikk, Jussi Ryynänen, Martti Voutilainen, 978-1-4799-3432-4/14/\$31.00 ©2014 IEEE

- [4] Parameterized All-Digital PLL Architecture and its Compiler to Support Easy Process Migration, Chao-Wen Tzeng, Shi-Yu Huang, Member, *IEEE*, and Pei-Ying Chao; *IEEE* transactions on very large scale integration (vlsi) systems, vol. 22, no. 3, march 2014 621

- [5] Design and VHDL Modeling of All-Digital PLLs, E. Zianbetov, M. Javidan, F. Anceau and D. Galayko,LIP6 Laboratory, Paris VI University, Paris, France, E. Colinet, Minatec Laboratory, CEA-LETI, Grenoble, France, J. Juillard, SSE Department, Supelec, Gif-Sur-Yvette, France

- [6] An All-Digital Phase-Locked Loop with Dynamic Phase Control for Fast Locking Yun-Chen Chuang, Sung-Lin Tsai, Cheng-En Liu, and Tsung-Hsien Lin, IEEE Asian Solid-State Circuits Conference November 12-14, 2012/Kobe, Japan

- [7] I. Hwang, S. Lee, S. Lee, and S. Kim, "A digitally controlled phaselocked loop with fast locking scheme for clock synthesis application," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2000, pp. 168–169.

- [8] T.-Y. Hsu, C.-C.Wang, and C.-Y. Lee, "Design and analysis of a portable high-speed clock generator," *IEEE Trans. Circuits Syst. II*, vol. 48, pp. 367–375, Apr. 2001.

- [9] J. Dunning, G. Garcia, J. Lundberg, and E. Nuckolls, "An all-digital phase-locked loop with 50-cycle lock time suitable for high-performance microprocessors," *IEEE J. Solid-State Circuits*, vol. 30, pp. 412–422, Apr. 1995.