# An Extensive Literature Review on Reversible Logic Gates

Shaik Mohammed Rafi<sup>1</sup>, Dr. J. L. Mazher Iqbal<sup>2</sup>, Dr. Chandra Mohan Reddy Sivappagari<sup>3</sup>

<sup>1</sup>Assistant professor. MallaReddy Engineering College for Women, Telanagana, India <sup>2</sup>Professor, Dept. of ECE, Madanapalle Institute of Technology and Science, Andhra Pradesh, India <sup>3</sup>Assistant Professor, Dept. of ECE, JNTUA College of Engineering, Pulivendula, Andhra Pradesh, India

Abstract- Reversible logic is promising as it can compute with different applications in low power like nanocomputing for instance quantum computing. Reversible circuits are similar to ordinary circuits notwithstanding they are work from reversible gates. Reversible circuits, have single, one-to-one mapping between the input and output vectors. A concise review of reversible logic gates basics will be studied. The basic reversible logic gates need to be optimized in reversible logic design and synthesis. Reversible gates need steady inputs for configuration of gate functions and junk outputs that helps in keeping reversibility. Consequently this research work would also cover the promising nanotechnologies.

*Index Terms*— Reversible logic gates, garbage output, quantum cost, power dissipation.

#### I. INTRODUCTION

Reversible logic is a promising computing plan worldview which displays a strategy for developing PCs that create no power dissipation. Reversible computing rose as an aftereffect of the utilization of quantum mechanics standards towards the improvement of an all inclusive computing machine. In particular, the basics of reversible computing depend on the relationship between entropy, heat move between atoms in a framework, the likelihood of a quantum molecule involving a specific state at any given time, and the quantum electrodynamics between electrons when they are in close vicinity. The fundamental guideline of reversible computing is that a bijective gadget with an indistinguishable number of input and output lines will deliver a computing domain where the electrodynamics of the framework take into consideration expectation of every single future state in view of known past states, and the framework achieves each conceivable state, bringing about no heat dissipation. A circuit is reversible when there is a one-to-one mapping

between sets of input and output values. Subsequently the estimations of input states can be constantly reproduced from the estimations of output states. Bennett's hypothesis proposes that every future (double) innovation will need to utilize a sort of reversible gates with a specific end goal to bring down the power dissipation. They can likewise use in quantum dots and DNA circuit realization technologies. The information and yield vector of a N-input and N- reversible logic gate or N X N reversible logic gate can indicated to as:

| $I_n = I1, I2, I3, \ldots, IN$ | (1) |

|--------------------------------|-----|

| $O_n = O1, 2, O3ON$            | (2) |

Here  $I_n$  and  $O_n$  speaks to input and output vectors of a reversible logic gate. The customary CMOS rationale gates are irreversible in nature as the information vectors can't be made by the output vectors. Therefore deleting a bit or loss of data causes *kTln2* joules of heat energy. However in reversible logic gates there exists a one of a kind coordinated mapping between the input and output vectors.

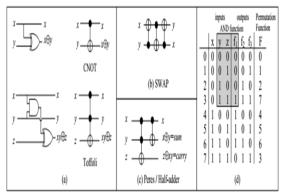

In programming and equipment uses of reversible data handling, successions of reversible operations can be seen as reversible circuits. For instance, swapping two values s x and y with an arrangement of three XOR or CNOT gates (appeared in Fig. 1a), operations  $x = x \bigoplus y$ ,  $y = x \bigoplus y$ , and  $x = x \bigoplus y$  is shown in Fig. 1b by a circuit. Such circuits are especially helpful in quantum computing. Reversibility forbids loops and explicit fanouts in circuits, 3 and every gate must have an equivalent number of inputs and yields with remarkable data to-yield assignments. Such exceptional elements of reversible circuits keep the utilization of existing algorithms and devices for circuit blend and streamlining. Reversible logic synthesis is the procedure of producing a minimized reversible circuit from a given detail. Research on reversible

logic synthesis has pulled in much consideration after the revelation of intense quantum calculations in the mid-1990s [Nielsen and Chuang 2000]. Firmly related methods have likewise been spurred by different applications, e.g., , e.g., the decomposition of permutations into tensor products is an important step in deriving fast algorithms and circuits for digital signal processing (Fourier and cosine transforms, etc.) [Egner et al. 1997].

This study talks about methodologies, algorithms, benchmarks, devices, open issues and future patterns identified with the blend of combinational reversible circuits.

Fig. 1. Expressing CNOT and Toffoli gates using AND and XOR gates (a), swapping two values x and y by three XOR operations (CNOT) as a reversible circuit (b), a reversible half-adder circuit (c), a sample reversible function (d).

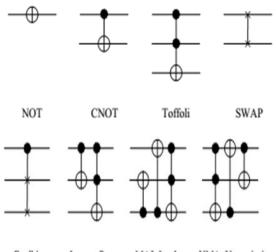

Fredkin Inverse Peres MAJ: In-place UMA: Un-majority majority and Add

Fig. 2. Basic reversible gates. The Peres gate (reversible half-adder) is defined in Fig. 1c. The MAJ and UMA gates together form a full-adder gate, used in [Cuccaro et al. 2005] to build reversible multi-bit adders.

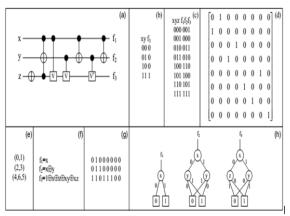

**A. Reversible gates.** A reversible gate realizes a reversible function. For a gate g, the gate g-1 implements the inverse transformation. Common reversible gates are illustrated in Fig. 2. Representation models. Reversible functions can be described in several ways, as illustrated in Fig. 3.

• **Truth tables**. The simplest method to describe a reversible function of size n is a truth table with n columns and 2n rows.

• Matrix representations. A Boolean reversible function (permutation) f can be described by a 0-1 matrix with a single 1 in each column and in each row (a permutation matrix), where the non-zero element in row i appears in column f(i). A different matrix representation for linear functions [Patel et al. 2008].

• **Reed-Muller expansion**. To denote a specification with algebraic formula, Positive polarity Reed-Muller (PPRM) expansion can be applied. PPRM expansion uses only uncomplemented variables and can be derived from the EXOR-Sum-of-Products (ESOP) description by replacing a' with a  $\bigoplus$  1 for a complemented variable a.

Fig. 3. A sample quantum circuit that implements a reversible specification (a), the specification in various formats: irreversible truth table (b), reversible truth table (c), matrix representation (d), cycle form (e), PPRM (f), RM spectrum (g), ROBDD (h).external

### II. LITERATURE SURVEY

In 1961, R.LANDAUER portrayed that the sensible irreversibility is connected with physical irreversibility and requires a negligible warmth era for each machine cycle. For irreversible logic calculations, every piece of data lost produces kTlog2 joules of heat energy, where k is Boltzmann's steady and T the supreme temperature at which calculation is performed. In customary

framework the great many gates used to perform consistent operations. Creator demonstrated that heat dissipation avoidable if framework made reversible [1].

In 1973, C.H.BENNETT depicted that if a calculation is done in Reversible rationale zero vitality dissemination is conceivable, as the measure of vitality scattered in a framework is specifically identified with the quantity of bits eradicated amid calculation. The outline that does not bring about data misfortune is irreversible. Arrangements of reversible gates are expected to plan reversible circuit. Reversible gate can produce remarkable output vector from every input vector and the other way around [2].

In 2008, Majid Mohammdi et.al exhibited those quantum gates to execute the parallel reversible rationale gates. Quantum gates V and V+ to be spoken to in truth table structures. Creator demonstrated that few reversible circuit benchmarks are enhanced and contrast and existing work. Another behavioral model to speak to the V and V+ quantum gates based on their properties. This model used to recreate the quantum realization of reversible circuits [3].

In 2010, D.Michael Mill operator and Zahra Sasanian exhibited the lessening the quantity of quantum gate expense of reversible circuits. To diminish the quantum cost enhances the proficiency of the circuit. To decide a quantum circuit is to first union circuits made out of parallel reversible gates then guide that circuit to a proportional quantum gate acknowledgment [4] CMOS, Quantum PC, Nanotechnology, Optical registering and self-repair [5].

In 2011, Md.Mazder Rahman et.al displayed a quantum gate library that comprises of all conceivable two-Qubit quantum gates which don't produce trapped states. These gates are utilized to decrease the quantum cost of reversible circuits. They proposed a two-qubit quantum entryway library that assumes a noteworthy part in decreasing the quantum expense of reversible gates [6].

In 2012, B.Raghu Kanth et.al depicted that actualizing of reversible circuit reducing garbage outputs, gate count and constant inputs, gates tally and consistent inputs. Expansion, Subtractions operations are acknowledged utilizing reversible DKG gate and it contrast and ordinary doors. The proposed reversible adder/subtractor circuit can be connected to outline of complex frameworks in nanotechnology [7].

In 2012, Mr. Devendra Goyal exhibited VHDL CODE of all Reversible Rationale Entryway, which give us to plan VHDL CODE of any complex successive circuit. Here creator have been attempted to make the VHDL code however much as could reasonably be expected. Creator can reenact and combination it utilizing Xilinx programming [8].

In 2013, Marek Szyprowski exhibited a device for minimizing the quantum cost in 4-bit reversible circuits. Here Creator demonstrated that for benchmarks and for plans taken from late distributions it is conceivable to acquire sparing in quantum cost contrasting and existing circuits [9].

In 2013, Raghava Garipelly gave that the essential reversible logic gates, which in planning of more intricate framework having reversible circuits as a primitive segment and this can execute more convoluted operations utilizing quantum computers. Creator presented some new gates which are BSCL, SBV, NCG, and PTR and so forth [10].

In 2014, Ashima Malhotra et.al portrayed that reversible adjusted Fredkin entryway used to plan the multiplexers with low quantum cost and contrast it and existing work. They likewise look at the quantum expense of multiplexers outline utilizing, Fredkin door with Changed Fredkin gate used to plan the multiplexers [11].

# III. PROPOSED FRAMEWORK

The proposed method may achieve the good performance of reversible gates in terms of cost, delay and logical output calculations. The gates were implemented in reversible arithmetic logic units in the existing research work. These new ALU designs are advantageous to previously work in synthesis that can favor low delay and high parameter calculation output, which is highly desirable for the realization of a reversible logic processing unit. The area and delay performance of ALU using reversible gates should be as low as possible.

# IV. CONCLUSION

Reversible computing has its great significance in reducing the complexity of the digital circuits. For this purpose various reversible logic gates are introduced by various researchers. In future, by using these gates we can design any of combinational or sequential circuit with numerous advantages over conventional gates such as, low power, low complexity, less delay, high speed etc.

### REFERENCES

[1] Landauer.R "Irreversibility and Heat Generation in the Computational Process", IBM Journal of Research and Development, 1961, Vol. No. 5, Issue No. 3, pp 183-191.

[2] Bennett C H "Logical Reversibility of Computation", IBM J. Research and Development, 1973, Vol. No.17, pp 525-532.

[3] Majid Mohammdi "Behavioral Model of V and V+ gates to implement the reversible circuits using quantum cost",2008, IEEE.

[4] D.Michael Miller and Zahra Sasanian, "Lowering the quantum gate cost of reversible circuits", IEEE, 2010.

[5] Prashant.R.Yelekar, "Introduction to reversible logic gates and its application", 2nd National Conference on Information and communication Technology, 2011.

[6] Md.Mazder Rahman, "Two-Qubit quantum gates to reduce the quantum cost of reversible circuit", IEEE International Symposium on multiple-valued logic, 2011.

[7] B.Raghu Kanth, "A Distinguish between reversible and conventional logic gates", International Journal of Engineering Research and Application, 2012, Vol. No.2, Issue No.2, pp.148-151.

[8] Mr. Devendra Goyal, Ms. Vidhi Sharma, "VHDL Implementation of Reversible Logic Gates", International Journal of Advanced Technology & Engineering Research (IJATER), 2012.

[9] Marek Szyprowski, "Reducing quantum cost in reversible Toffoli circuits", IEEE, 2013.

[10] Raghava Garipelly, P.Madhu Kiran, A.Santhosh Kumar, "A Review on Reversible Logic Gates and their Implementation", International Journal of Emerging Technology and Advanced Engineering, March 2013, Vol. No. 3, Issue No. 3.

[11] Ashima Malhotra, Charanjit Singh, Amandeep Singh, "Efficient Design of Reversible Multiplexers with Low Quantum Cost", International Journal of Engineering Research and Applications, Volume 4, Issue 7, July 2014.pp.20-23.

# BIO DATA

Shaik Mohammed Rafi, presently working as Assistant Professor, Department of ECE, MallaReddy Engineering College for women, Telanagana, India.

Co-Author-1

**Dr.J.L.Mazher Iqbal** received Ph.D in year 2013. Presently working as Professor, Dept.of ECE in Madanapalle Institute of Technology and Science, Andhra Pradesh, India. **Co-Author-2**

**Chandra Mohan Reddy Sivappagari** received Ph.D in year 2014. Presently working as Assistant Professor, Dept.of ECE in JNTUA College of Engineering, Pulivendula, Andhra Pradesh, India.